浙江江蘇半導體封裝公司

先進芯片封裝技術-2.5D/3D封裝:2.5D封裝技術可將多種類型芯片放入單個封裝,通過硅中介層實現信號橫向傳送,提升封裝尺寸和性能,需用到硅通孔(TSV)、重布線層(RDL)、微型凸塊等主要技術。3D封裝則是在垂直方向疊放兩個以上芯片,直接在芯片上打孔和布線連接上下層芯片堆疊,集成度更高。中清航科在2.5D/3D封裝技術方面持續創新,已成功應用于高性能計算、人工智能等領域,幫助客戶實現芯片性能的跨越式提升。有相關需求歡迎隨時聯系。中清航科芯片封裝技術,支持系統級封裝,實現芯片與被動元件一體化。浙江江蘇半導體封裝公司

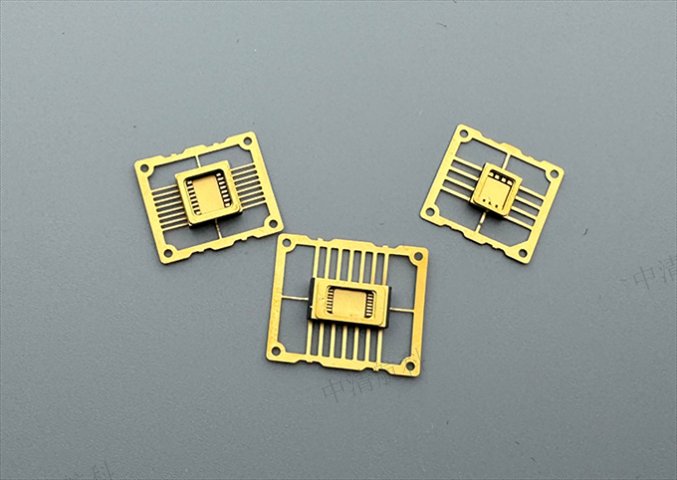

針對車規級芯片AEC-Q100認證痛點,中清航科建成零缺陷封裝產線。通過銅柱凸點替代錫球焊接,結合環氧模塑料(EMC)三重防護層,使QFN封裝產品在-40℃~150℃溫度循環中通過3000次測試。目前已有17家Tier1供應商采用其AEC-QGrade1封裝解決方案。中清航科多芯片重構晶圓(ReconstitutedWafer)技術,將不同尺寸芯片集成于300mm載板。通過動態貼裝算法優化芯片排布,材料利用率提升至92%,較傳統WLCSP降低成本28%。該方案已應用于物聯網傳感器批量生產,單月產能達500萬顆。sot89封裝中清航科芯片封裝工藝,通過低溫鍵合技術,保護芯片內部敏感元件。

中清航科部署封裝數字孿生系統,通過AI視覺檢測實現微米級缺陷捕捉。在BGA植球工藝中,球徑一致性控制±3μm,位置精度±5μm。智能校準系統使設備換線時間縮短至15分鐘,產能利用率提升至90%。針對HBM內存堆疊需求,中清航科開發超薄芯片處理工藝。通過臨時鍵合/解鍵合技術實現50μm超薄DRAM晶圓加工,4層堆疊厚度400μm。其TSV深寬比達10:1,阻抗控制在30mΩ以下,滿足GDDR6X1TB/s帶寬要求。中清航科可拉伸封裝技術攻克可穿戴設備難題。采用蛇形銅導線與彈性體基底結合,使LED陣列在100%拉伸形變下保持導電功能。醫療級生物相容材料通過ISO10993認證,已用于動態心電圖貼片量產。

芯片封裝的發展歷程:自20世紀80年代起,芯片封裝技術歷經多代變革。從早期的引腳插入式封裝,如DIP(雙列直插式封裝),發展到表面貼片封裝,像QFP(塑料方形扁平封裝)、PGA(針柵陣列封裝)等。而后,BGA(球柵陣列封裝)、MCP(多芯片模塊)、SIP(系統級封裝)等先進封裝形式不斷涌現。中清航科緊跟芯片封裝技術發展潮流,不斷升級自身技術工藝,在各個發展階段都積累了豐富經驗,能為客戶提供符合不同時期技術標準和市場需求的封裝服務。微型芯片封裝難度大,中清航科微縮技術,實現小體積承載強性能。

中清航科超細間距倒裝焊工藝突破10μm極限。采用激光輔助自對準技術,使30μm微凸點對位精度達±1μm。在CIS圖像傳感器封裝中,該技術消除微透鏡偏移問題,提升低光照下15%成像質量。中清航科開發出超薄中心less基板,厚度100μm。通過半加成法(mSAP)實現2μm線寬/間距,傳輸損耗低于0.3dB/mm@56GHz。其5G毫米波AiP天線封裝方案已通過CTIAOTA認證,輻射效率達72%。為響應歐盟RoHS2.0標準,中清航科推出無鉛高可靠性封裝方案。采用Sn-Bi-Ag合金凸點,熔點138℃且抗跌落性能提升3倍。其綠色電鍍工藝使廢水重金屬含量降低99%,獲三星Eco-Partner認證。中清航科聚焦芯片封裝,用綠色工藝,降低生產過程中的能耗與排放。浙江江蘇半導體封裝公司

中清航科芯片封裝團隊,攻克精密焊接難題,保障芯片內部連接穩定。浙江江蘇半導體封裝公司

中清航科MIL-STD-883認證產線實現金錫共晶焊接工藝。在宇航級FPGA封裝中,氣密封裝漏率<5×10??atm·cc/s,耐輻照總劑量達100krad。三防涂層通過96小時鹽霧試驗,服務12個衛星型號項目。中清航科推出玻璃基板中介層技術,介電常數低至5.2@10GHz。通過TGV玻璃通孔實現光子芯片與電芯片混合集成,耦合損耗<1dB。該平臺已用于CPO共封裝光學引擎開發,傳輸功耗降低45%。中清航科建立全維度失效分析實驗室。通過3DX-Ray實時監測BGA焊點裂紋,結合聲掃顯微鏡定位分層缺陷。其加速壽命測試模型可精確預測封裝產品在高溫高濕(85℃/85%RH)條件下的10年失效率。浙江江蘇半導體封裝公司

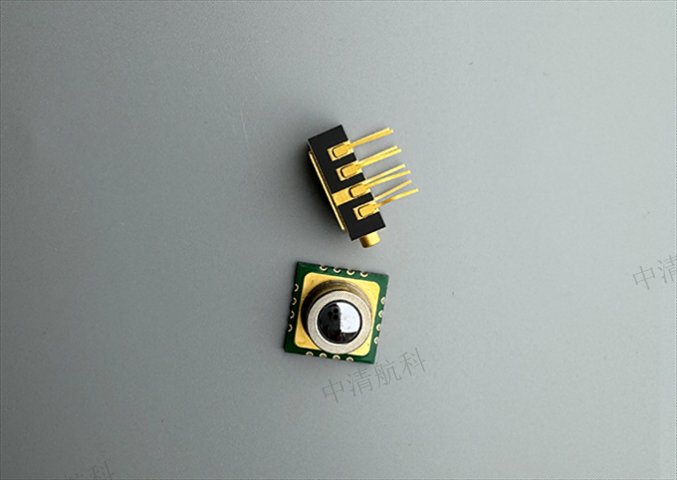

- cis傳感器封裝 2025-12-21

- 芯片級封裝(chip scale package) 2025-12-21

- 南通芯片晶圓切割藍膜 2025-12-20

- 12英寸半導體晶圓切割企業 2025-12-20

- 衢州碳化硅陶瓷晶圓切割刀片 2025-12-20

- 衢州碳化硅半導體晶圓切割代工廠 2025-12-20

- 鹽城碳化硅晶圓切割藍膜 2025-12-20

- 浙江芯片級封裝(chip scale package) 2025-12-20

- 江蘇碳化硅線晶圓切割廠 2025-12-20

- 上海氣體傳感器陶瓷封裝 2025-12-20

- 玄武區購買網站建設 2025-12-21

- 海南購買商管ERP軟件怎么選 2025-12-21

- 廈門小區電動車充電樁加盟方式 2025-12-21

- 金山區挑選AUTOSAR工具鏈服務電話 2025-12-21

- 東莞3600dpi彩膜UV打印機制造商 2025-12-21

- 全椒短視頻營銷合作 2025-12-21

- eaory證卡打印機 耗材 2025-12-21

- 北京網絡服務器機箱品牌 2025-12-21

- 佛山高精度電器按鍵面板UV打印機行價 2025-12-21

- 實時專利智能撰寫平臺 2025-12-21