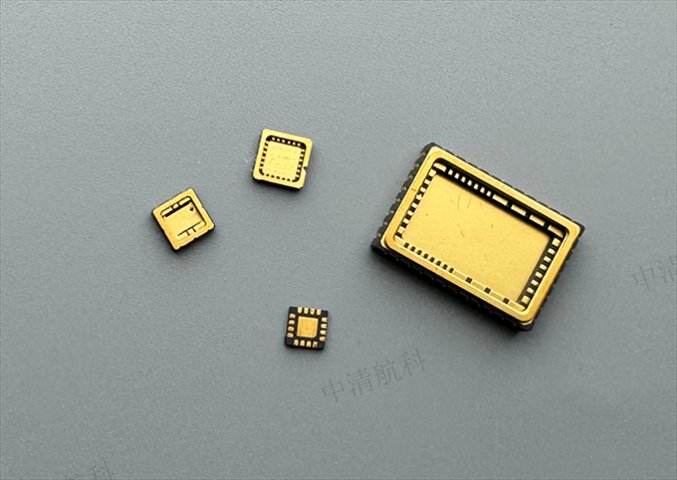

dfn封裝設計

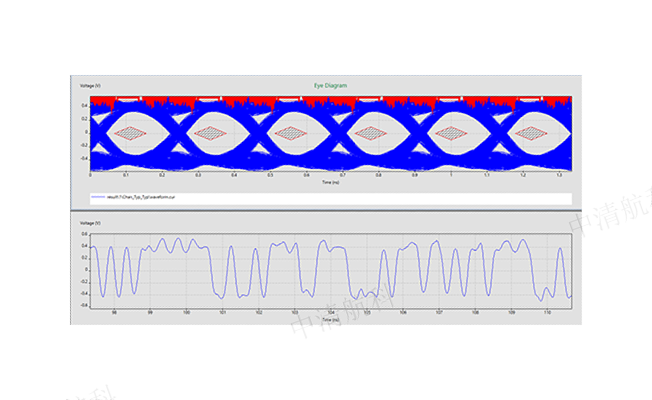

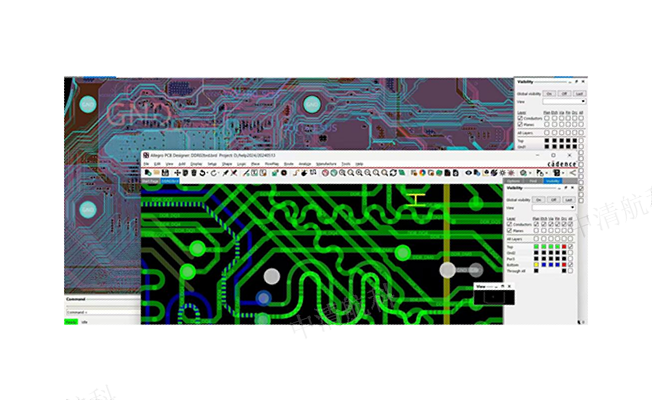

隨著摩爾定律逼近物理極限,先進封裝成為提升芯片性能的關鍵路徑。中清航科在Fan-Out晶圓級封裝(FOWLP)領域實現突破,通過重構晶圓級互連架構,使I/O密度提升40%,助力5G射頻模塊厚度縮減至0.3mm。其開發的激光解鍵合技術將良率穩定在99.2%以上,為毫米波通信設備提供可靠封裝方案。面對異構集成需求激增,中清航科推出3DSiP立體封裝平臺。該方案采用TSV硅通孔技術與微凸點鍵合工藝,實現CPU、HBM內存及AI加速器的垂直堆疊。在數據中心GPU領域,其散熱增強型封裝結構使熱阻降低35%,功率密度提升至8W/mm2,滿足超算芯片的嚴苛要求。中清航科芯片封裝方案,通過模塊化接口,簡化下游廠商應用難度。dfn封裝設計

針對TMR傳感器靈敏度,中清航科開發磁屏蔽封裝。坡莫合金屏蔽罩使外部場干擾<0.1mT,分辨率達50nT。電流傳感器精度達±0.5%,用于新能源汽車BMS系統。中清航科微型熱電發生器實現15%轉換效率。Bi?Te?薄膜與銅柱互聯結構使輸出功率密度達3mW/cm2(ΔT=50℃)。物聯網設備實現供能。中清航科FeRAM封裝解決數據保持難題。鋯鈦酸鉛薄膜與耐高溫電極使1012次讀寫后數據保持率>99%。125℃環境下數據保存超10年,適用于工業控制存儲。江蘇金屬陶瓷封裝中清航科深耕芯片封裝,從設計到量產全流程優化,縮短產品上市周期。

針對車規級芯片AEC-Q100認證痛點,中清航科建成零缺陷封裝產線。通過銅柱凸點替代錫球焊接,結合環氧模塑料(EMC)三重防護層,使QFN封裝產品在-40℃~150℃溫度循環中通過3000次測試。目前已有17家Tier1供應商采用其AEC-QGrade1封裝解決方案。中清航科多芯片重構晶圓(ReconstitutedWafer)技術,將不同尺寸芯片集成于300mm載板。通過動態貼裝算法優化芯片排布,材料利用率提升至92%,較傳統WLCSP降低成本28%。該方案已應用于物聯網傳感器批量生產,單月產能達500萬顆。

先進芯片封裝技術-2.5D/3D封裝:2.5D封裝技術可將多種類型芯片放入單個封裝,通過硅中介層實現信號橫向傳送,提升封裝尺寸和性能,需用到硅通孔(TSV)、重布線層(RDL)、微型凸塊等主要技術。3D封裝則是在垂直方向疊放兩個以上芯片,直接在芯片上打孔和布線連接上下層芯片堆疊,集成度更高。中清航科在2.5D/3D封裝技術方面持續創新,已成功應用于高性能計算、人工智能等領域,幫助客戶實現芯片性能的跨越式提升。有相關需求歡迎隨時聯系。中清航科芯片封裝工藝,通過仿真優化,提前規避量產中的潛在問題。

中清航科的技術合作與交流:為保持技術為先,中清航科積極開展技術合作與交流。公司與國內外高校、科研院所建立產學研合作關系,共同開展芯片封裝技術研究;參與行業技術研討會、標準制定會議,分享技術經驗,了解行業動態。通過技術合作與交流,公司不斷吸收先進技術和理念,提升自身技術水平,為客戶提供更質優的技術服務。芯片封裝的失效分析與解決方案:在芯片使用過程中,可能會出現封裝失效的情況。中清航科擁有專業的失效分析團隊,能通過先進的分析設備和技術,準確找出封裝失效的原因,如材料缺陷、工藝問題、使用環境不當等。針對不同的失效原因,公司會制定相應的解決方案,幫助客戶改進產品設計或使用方式,提高產品可靠性,減少因封裝失效帶來的損失。穿戴設備芯片需輕薄,中清航科柔性封裝,適配人體運動場景需求。江蘇先進陶瓷封裝

中清航科芯片封裝工藝,引入納米涂層技術,提升芯片表面防護能力。dfn封裝設計

中清航科芯片封裝的應用領域-通信領域:在5G通信時代,對芯片的高速率、低延遲、高集成度等性能要求極高。中清航科憑借先進的芯片封裝技術,為5G基站的射頻芯片、基帶芯片等提供質優封裝服務,有效提升了芯片間的通信速度和數據處理能力,滿足了5G通信對高性能芯片的嚴苛需求,助力通信行業實現技術升級和網絡優化。中清航科芯片封裝的應用領域-消費電子領域:消費電子產品如智能手機、平板電腦、智能穿戴設備等,對芯片的尺寸、功耗和性能都有獨特要求。中清航科針對消費電子領域的特點,運用晶圓級封裝、系統級封裝等技術,為該領域客戶提供小型化、低功耗且高性能的芯片封裝解決方案,使消費電子產品在輕薄便攜的同時,具備更強大的功能和更穩定的性能。dfn封裝設計

- 南通芯片晶圓切割藍膜 2025-12-20

- 12英寸半導體晶圓切割企業 2025-12-20

- 衢州碳化硅陶瓷晶圓切割刀片 2025-12-20

- 衢州碳化硅半導體晶圓切割代工廠 2025-12-20

- 鹽城碳化硅晶圓切割藍膜 2025-12-20

- 浙江芯片級封裝(chip scale package) 2025-12-20

- 江蘇碳化硅線晶圓切割廠 2025-12-20

- 上海氣體傳感器陶瓷封裝 2025-12-20

- 國產芯片封裝廠家 2025-12-20

- 紹興碳化硅線晶圓切割企業 2025-12-20

- 無錫進口保護殼推薦廠家 2025-12-20

- 普陀區各種市場營銷策劃 2025-12-20

- 清遠質量小間距LED屏 2025-12-20

- 江蘇特色保護殼市面價 2025-12-20

- 廣西貨代管理軟件哪些不要錢 2025-12-20

- 天津四探頭激光雷達價位 2025-12-20

- 來安模塊化弱電智能化集成服務 2025-12-20

- 貿易金蝶云星瀚方法 2025-12-20

- 金華迷你無線掃描槍 2025-12-20

- 云南推薦的無人機飛控系統 2025-12-20